- 您现在的位置:买卖IC网 > Sheet目录3880 > PIC16F785-I/SO (Microchip Technology)IC PIC MCU FLASH 2KX14 20SOIC

106

8272E–AVR–04/2013

ATmega164A/PA/324A/PA/644A/PA/1284/P

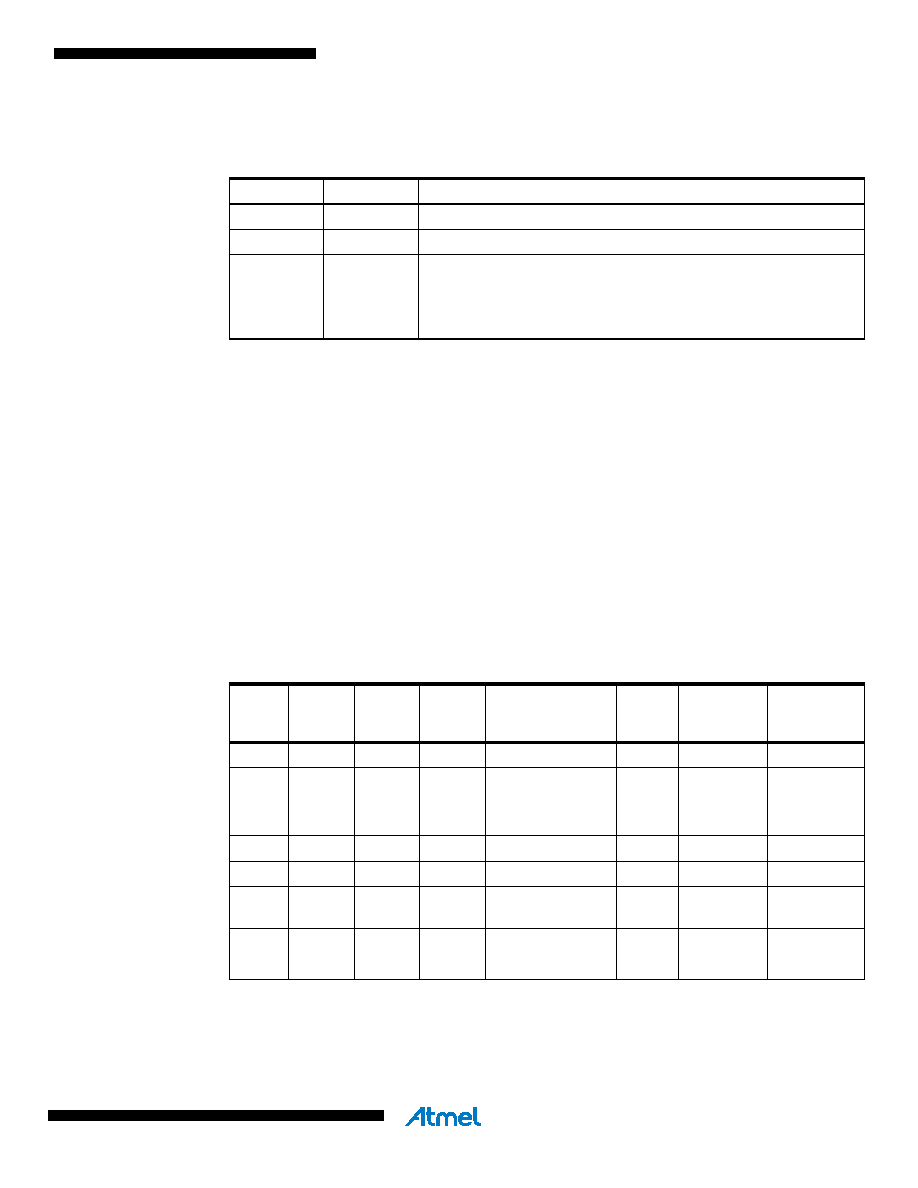

Table 15-7 on page 106 shows the COM0B1:0 bit functionality when the WGM02:0 bits are set

to phase correct PWM mode.

Note:

1. A special case occurs when OCR0B equals TOP and COM0B1 is set. In this case, the Com-

pare Match is ignored, but the set or clear is done at TOP. See ”Phase Correct PWM mode” on

page 101 for more details.

Bits 3:2 – Reserved

These bits are reserved bits in the Atmel

ATmega164A/164PA/324A/324PA/644A/644PA/1284/1284P and will always read as zero.

Bits 1:0 – WGM01:0: Waveform Generation mode

Combined with the WGM02 bit found in the TCCR0B Register, these bits control the counting

sequence of the counter, the source for maximum (TOP) counter value, and what type of wave-

form generation to be used, see Table 15-8 on page 106. Modes of operation supported by the

Timer/Counter unit are: Normal mode (counter), Clear Timer on Compare Match (CTC) mode,

and two types of Pulse Width Modulation (PWM) modes (see ”Modes of Operation” on page

Notes:

1. MAX

= 0xFF

2. BOTTOM = 0x00

Table 15-7.

Compare Output mode, Phase Correct PWM mode (1).

COM0B1

COM0B0

Description

0

Normal port operation, OC0B disconnected.

01

Reserved

10

Clear OC0B on Compare Match when up-counting. Set OC0B on

Compare Match when down-counting.

11

Set OC0B on Compare Match when up-counting. Clear OC0B on

Compare Match when down-counting.

Table 15-8.

Waveform Generation mode bit description.

Mode

WGM2

WGM1

WGM0

Timer/Counter

mode of

operation

TOP

Update of

OCRx at

TOV Flag

set on

0

Normal

0xFF

Immediate

MAX

10

0

1

PWM, Phase

Correct

0xFF

TOP

BOTTOM

2

0

1

0

CTC

OCRA

Immediate

MAX

3

0

1

Fast PWM

0xFF

BOTTOM

MAX

4

1

0

Reserved

–

51

0

1

PWM, Phase

Correct

OCRA

TOP

BOTTOM

6

1

0

Reserved

–

7

1

Fast PWM

OCRA

BOTTOM

TOP

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

PIC16C56A-04/SO

IC MCU OTP 1KX12 18SOIC

PIC18F23K20-I/MV

IC MCU 8BIT 8KB FLASH 28UQFN

PIC16F627A-I/P

IC MCU FLASH 1KX14 EEPROM 18DIP

XF2G-1414-11

CONN FPC 14POS 0.5MM SMT

PIC16F777T-I/ML

IC PIC MCU FLASH 8KX14 44QFN

PIC18F2539T-E/SO

IC PIC MCU FLASH 12KX16 28SOIC

PIC16LF1936-I/SO

IC PIC MCU FLASH 512KX14 28-SOIC

PIC16F873AT-E/ML

IC PIC MCU FLASH 4KX14 28QFN

相关代理商/技术参数

PIC16F785-I/SS

功能描述:8位微控制器 -MCU 3.5KB FL 128R 18 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F785T-E/SS

功能描述:8位微控制器 -MCU 3.5KB FL 128R 18 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F785T-I/ML

功能描述:8位微控制器 -MCU 3.5 KB 128 RAM 18I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F785T-I/ML036

制造商:Microchip Technology Inc 功能描述:

PIC16F785T-I/ML045

制造商:Microchip Technology Inc 功能描述:

PIC16F785T-I/SO

功能描述:8位微控制器 -MCU 3.5KB FL 128R 18 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F785T-I/SS

功能描述:8位微控制器 -MCU 3.5KB FL 128R 18 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F818-E/ML

功能描述:8位微控制器 -MCU 1.75KB 128RAM 16 I/O Ext Temp QFN28 RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT